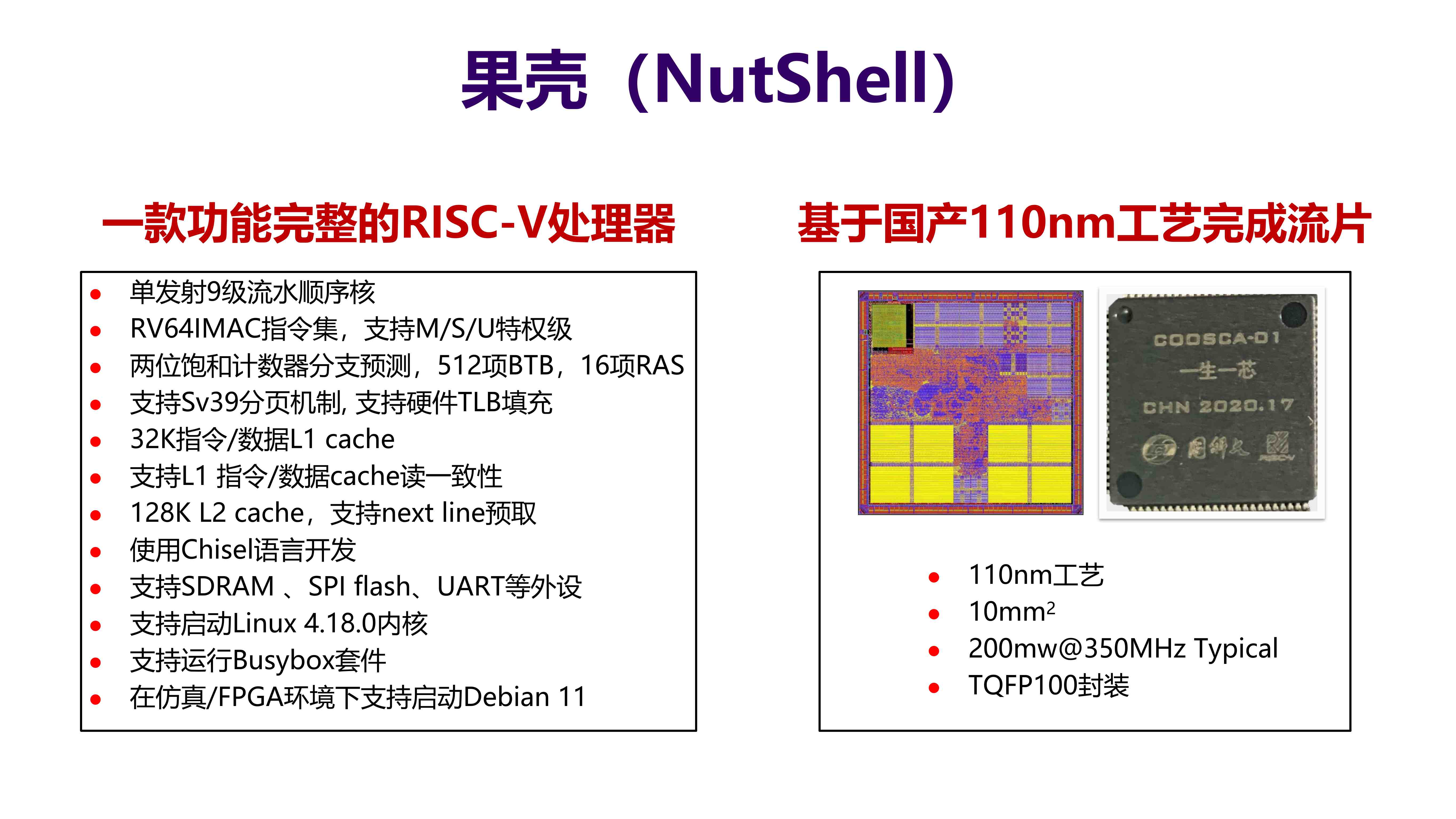

Review of past sessions

The 1st session

On August 27, 2019, five 2016 undergraduate students from the University of Chinese Academy of Sciences and the teaching team held a relaxed but significant mobilization meeting in the office of Professor Bao Yungang. At the meeting, they discussed and formulated the overall design plan for the processor chip, determined the technical route, basic platform, development environment, tape-out process, etc. At this point, the first session of the "One Student One Chip" Initiative was officially launched. Subsequently, during the 4 months intensive development process, five students, under the leadership of the teaching team, were responsible for implementing each core functional module of the processor chip. Although a lot of professional knowledge was not introduced in class, the students independently reviewed the information and solved various problems encountered during development.Finally, through the joint efforts of the students and the teaching team, the first session of the "One Student One Chip" processor chip was successfully lit, and was able to successfully run the GNU/Linux operating system and print the logo of UCAS on the terminal.

The 2nd session

The second session of the "One Student One Chip" Initiative was officially launched in the fall of 2020. The student composition is no longer limited to undergraduates from the University of Chinese Academy of Sciences, but has successfully attracted a total of 11 outstanding students from Zhejiang University, Nanjing University, Northwestern Polytechnical University, Harbin Institute of Technology (Shenzhen) and other universities to sign up. In addition to the increase in the number of participants in the initiative, the staffing of the second session of the "One Student One Chip" teaching team has also been further upgraded. Two teachers from the ICT and Zhejiang University have joined the teaching team, and six 2016 UCAS undergraduate students have served as TAs (including the first 5 students from the first session of the "One Student One Chip" Initiative and one student in charge of the FPGA simulation platform provide technical guidance to students in this session at key development nodes. Finally, after several months of independent development and debugging verification, 11 students all completed the processor core design and tape-out.

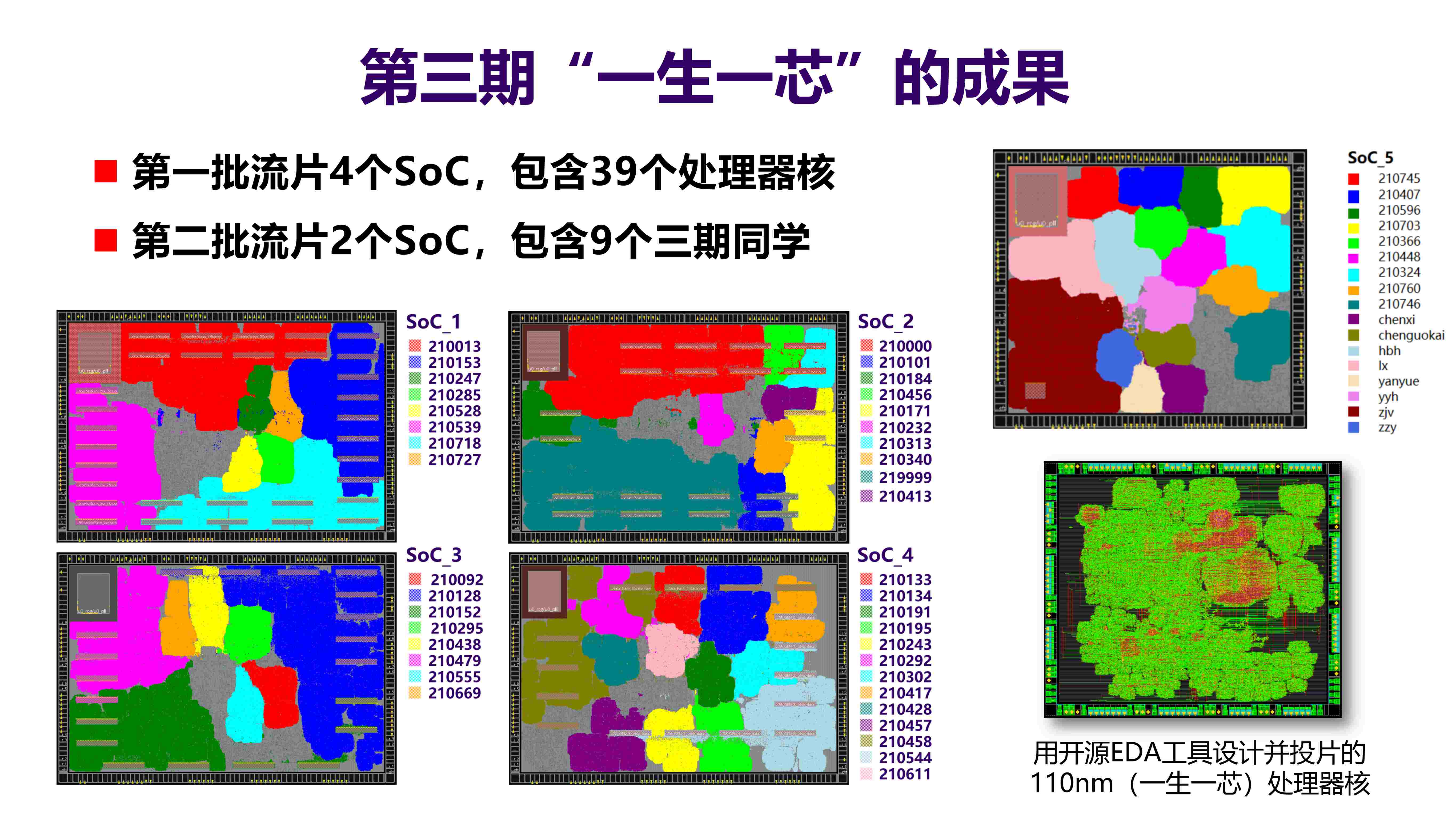

The 3rd session

The third session of the "One Student One Chip" Initiative was officially launched on July 7, 2021. It strives to combine the training of processor chip design talents with the construction of an open source processor chip ecosystem, and cultivate both masters of knowledge in the field of processor chip architecture design. Professional talents who have experience in the entire process of processor chip design and manufacturing. The total number of applicants for the third session is 760, and participating students cover 168 domestic and foreign universities (including 30 foreign universities). According to statistics from the student's perspective, among the number of applicants, there are 625 current students, accounting for 82%. At the same time, many graduated students are also interested in processor chip design. Among the students on campus, undergraduates, masters and doctoral students are distributed in all grades, of which 44% are undergraduates, 50% are master students, and 6% are masters and doctoral students. In terms of grade breakdown, the five grades with the most applicants are: first-year graduate students (27%), junior students (23%), second-year graduate students (14%), sophomore students (11%), and senior students (7%). Judging from the registration data, the third session of the "One Student One Chip" Initiative has officially entered the cross-regional large-scale talent training stage.

In order to cope with the huge challenges in labor costs brought about by large-scale talent training, the project team tried for the first time to establish a set of teaching processes that "let students guide students". Lecture Q&A, progress inspection, SoC integration verification and back-end physical design are all completed independently by the students. Engineers only participate in the inspection of the chip back-end in the final stage and make suggestions for improvement. This not only fundamentally solves the problem of imbalance between supply and demand of teachers, but also cultivates a group of TA teams with excellent technical skills and excellent psychological quality, laying a solid foundation for the subsequent development of the "One Student One Chip" Initiative. There are 27 front-end TAs in total, who are mainly responsible for preparing lecture notes and other auxiliary materials, organizing reports and answering questions, and following up on students' learning progress. The SoC team has 4 people, mainly responsible for collecting processor codes submitted by students and performing SoC integration and post-integration verification work. The IC back-end team has a total of 5 people, mainly responsible for the physical design of the chip and generating a GDSII layout that can be taped out. With the support of the above process, the number of tape-out students in this session has reached more than 50.

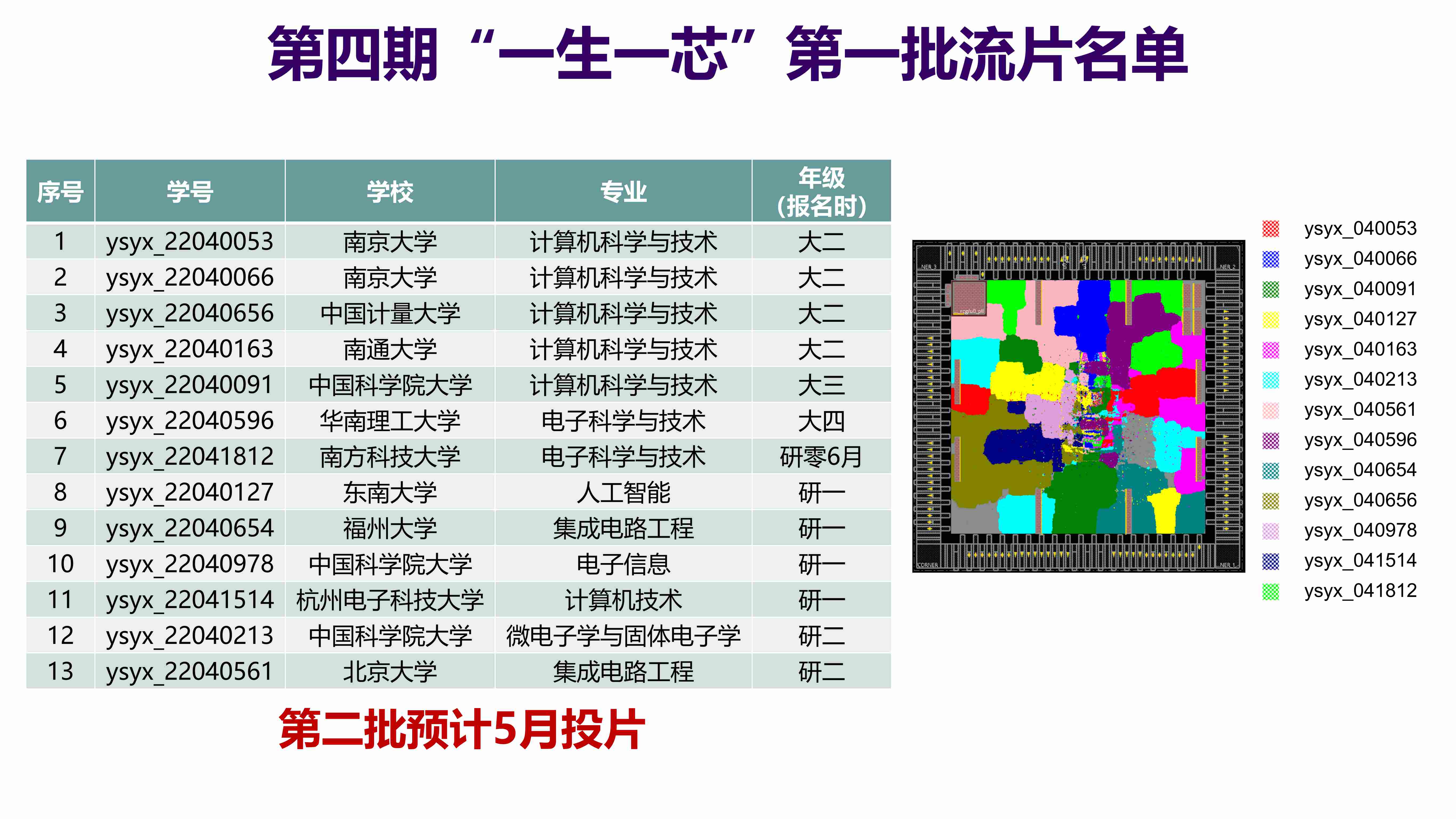

The 4th session

After learning from the valuable experiences summarized by students who participated in the third session of the initiative, the project team sorted out the goals of the fourth session of the "One Student One Chip" Initiative and clarified the three-step strategy of the "One Student One Chip" Initiative. The first step is to break the barriers of imbalanced educational resources, so that those college students from both sides of the country who are very interested in processor chip design can also have the opportunity to participate in the full-process learning of processor chips. This has very important and positive significance for improving the popularization of processor chip education in colleges and universities in my country. The second step is to break through the boundaries of traditional courses and integrate EE and CS for full-stack talent training. The core of the fourth session of the"One Student One Chip" Initiative is to build a set of software and hardware co-design concepts and integrate them into the entire processor chip teaching process so that students not only understand how to design processor chips with code , but also to understand how processor chips are made, that is, the entire process of processor chips from design to manufacturing. The third step is to encourage students who have participated in the program to enter the software and hardware open source community and strive to overcome various bottleneck problems that our country currently needs to solve. In stuck areas, major breakthroughs in key areas will ultimately attract more students to participate in the "One Student One Chip" Initiative, thus achieving a virtuous positive cycle.

The number of applicants for the fourth session of "One Student One Chip" was 1,753, covering a total of 328 colleges and universities at home and abroad. The number of applicants increased by 130.0% compared with the previous session, and the growth rate of college coverage was 95.2%. This shows that with the progress of third session of "One Student One Chip" Initiative, more students recognized the large-scale talent training plan proposed by the teaching team, and the scale of teaching began to gradually expand. The fourth session of the "One Student One Chip" Initiative is divided into four training stages, of which a total of 98 people have studied to stage B, a total of 101 people have studied to stage A, a total of 16 people have completed the tape-out through defense, and a total of 215 people have continued to study. People, despite increasing the difficulty of learning, the number of students continuing to study this period has basically remained the same as that of the previous session. And as the learning stage deepens, there is no obvious one-sided situation in the number of undergraduates and graduate students. This shows that whether you are just starting students with zero-based in professional knowledge or scholars who have already engaged in research in related fields can adapt well to the training program provided by "One Student One Chip".

The 5th session

As of now, the number of applicants for the fifth session of "One Student One Chip" is 1,744, and the coverage of universities, the proportion of disciplines and majors, and the number of people who have passed the tape-out are basically consistent with the previous session. Compared with the previous sessions, there are two biggest highlights of the fifth session of the "One Student One Chip" Initiative: First, the teaching team has added new teaching courseware and videos based on the study handouts of the fourth session. The learning slope is further slowed down, allowing students to complete various stages of processor chip design step by step. Secondly, for the first time, there are students in high school and below among the registered students, and the number has reached 22, which indicates that the continuously optimized"One Student One Chip" Initiative training program will be more universal: Facts have proved regardless of the age of the students, as long as they love processor chip design and have the most basic understanding of computer software and hardware, they can participate in the "One Student One Chip" Initiative and achieve quite good results. At the same time, it can be seen that the attraction and influence of the "One Student One Chip" Initiative is increasing day by day. We believe that as time goes by, "One Student One Chip"" will enable every student to learn something and have the opportunity to achieve it. The ultimate goal is to graduate with a processor chip designed by themselves.

The first batch of tape-out list for the fifth session of "One Student One Chip"

| No. | Student ID | School | Major | Grade |

|---|---|---|---|---|

| 1 | ysyx_22050228 | Northeastern University | Electronic Science and Technology | Junior |

| 2 | ysyx_22050133 | Peking University | Mechanical | The 2nd year of graduate |

| 3 | ysyx_22050920 | Hangzhou Dianzi University | Electronic Science and Technology | Senior |

| 4 | ysyx_22040501 | Harbin Institute of Technology | Information and Communication Engineering | The 1st year of graduate |

| 5 | ysyx_22040502 | Beijing Institute of Technology | Electronic Information | Junior |

| 6 | ysyx_22041461 | Sichuan University | Microelectronics Science and Engineering | Junior |

| 7 | ysyx_22050550 | Nanjing University | Microelectronics and Solid State Electronics | The 1st year of graduate |

| 8 | ysyx_22040750 | Nanjing University | Electronic Science and Technology | The 1st year of PhD |

| 9 | ysyx_22040318 | TongJi University | Computer | The 2nd year of graduate |

| 10 | ysyx_22051098 | Chinese Academy of Sciences University | Computer Science and Technology | Junior |

| 11 | ysyx_22051110 | Chinese Academy of Sciences University | Computer Science and Technology | Junior |

| 12 | ysyx_22051094 | Chinese Academy of Sciences University | Computer Science and Technology | Junior |

| 13 | ysyx_22050369 | Hubei University | Electronic Information | The 2nd year of graduate |

| 14 | ysyx_22051106 | Chinese Academy of Sciences University | Computer Science and Technology | Junior |

| 15 | ysyx_22051085 | University of Chinese Academy of Sciences | Computer Science and Technology | Junior |